axis

np.stack(x_new, axis=-2)

### np.stack(x_new, axis=-2) 在函数中,`x_new = np.stack(x_new, axis=-2)` 的目的是将保留区域的 `x` 数组沿着倒数第二个维度进行堆叠,得到一个新的数组 `x_new`,该数组的维度为 `(6940, 45, 90, a, 9)`,其中 ......

AMBA4 AXI-Lite

- 参考 - https://zhuanlan.zhihu.com/p/49834243 *** ## 关于AXI-Lite - 相较于AXI4,有何不同 - 突发传输的长度固定为1. - 数据位宽固定为32位或者64位,也不支持在指定位宽通道上传输更小位宽的数据。 - 所有的访问都是不可修改的(N ......

AMBA4 AXI - 原子操作的锁定访问 & 独占访问

- 参考 - https://www.cnblogs.com/pu1se/p/16707862.html - https://blog.csdn.net/zmfmfking/article/details/120081488 *** ## 1. 锁访问 - [这篇博客](https://www.cn ......

AMBA4 AXI-Stream

- 参考 - https://zhuanlan.zhihu.com/p/152283168 - https://zhuanlan.zhihu.com/p/540870100 *** ## 1. 关于AXI-Stream - 数据流的处理一般和DMA一起使用,对数据位宽的对齐处理和流传输方式更关注。 ......

AMBA4 AXI 多主机多传输

- 参考 - https://zhuanlan.zhihu.com/p/149112312 *** ## 1. 多主机 AXI 架构  - [这篇博客](https://www.cnblogs.com/qianbinbin/p/17466180.html)中提到, ......

axis2 maven报错Could not find artifact org.apache.axis2:axis2:jar:1.7.9

Could not find artifact org.apache.axis2:axis2:jar:1.8.2 in aliyunmaven (https://maven.aliyun.com/repository/public/) 一开始以为是镜像的问题,但是换成中央仓库也没用 实际上,这个目录 ......

从 sum 求和谈 axis=1 or 0

## 二维数组 `axis=0`:表示从上往下 `axis=1`:表示从左往右  ```python temp = ......

AMBA4 AXI 相关理解(二)

- 参考 - https://zhuanlan.zhihu.com/p/45122977 *** ## 1. 五个独立通道 - 只支持单向传输,由主机发起读写请求。 - 通道分别为: - 写数据 W - 写地址 AW - 读数据 R - 读地址 AR - 写回复 R - 没有读回复通道的原因:读回复 ......

AMBA4 AXI 相关理解(一)

- 参考 - https://zhuanlan.zhihu.com/p/166419540 - https://zhuanlan.zhihu.com/p/44766356 *** ## 1. AXI总线的三个分类 - AXI4:地址映射控制,大块数据读写。如DDR、BRAM数据搬移等。 - AXI- ......

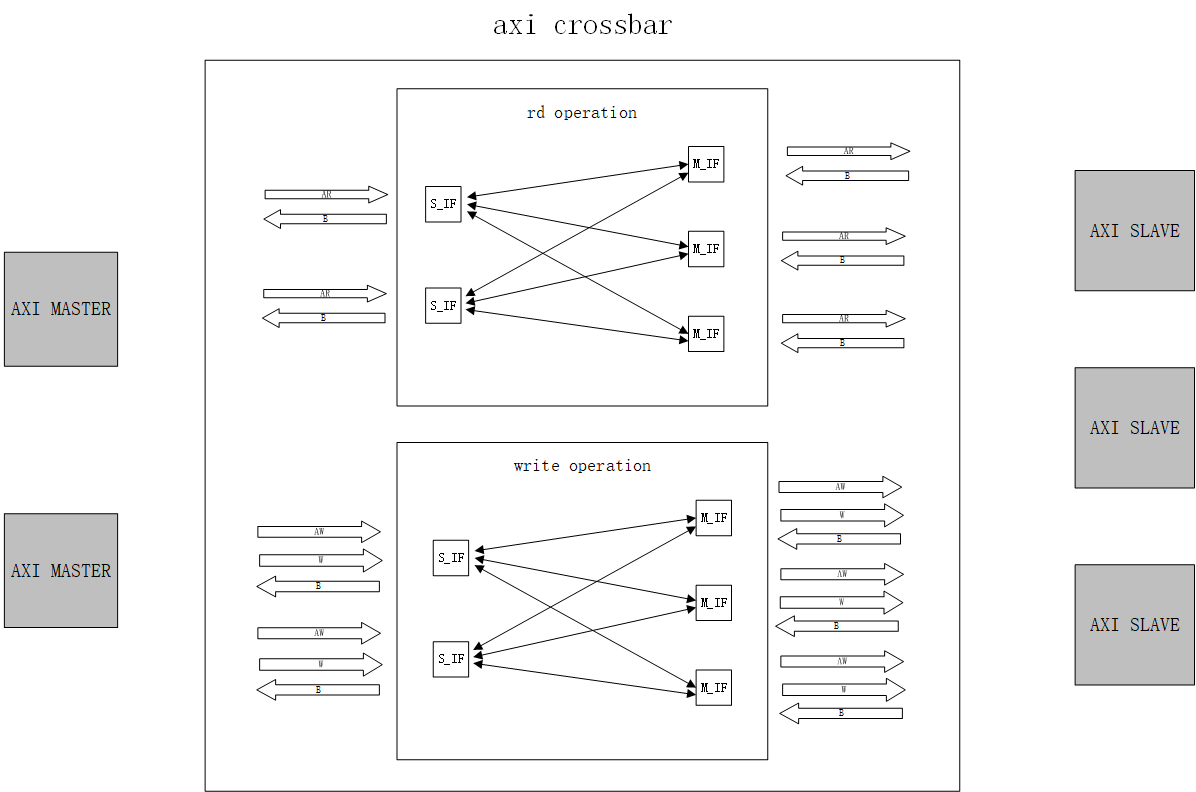

axi_crossbar IP使用说明

#总体简介  图例是2X3的配置 #主要特性 ▲支持Master、Slave接口数量配置 ▲支持全连接、部 ......

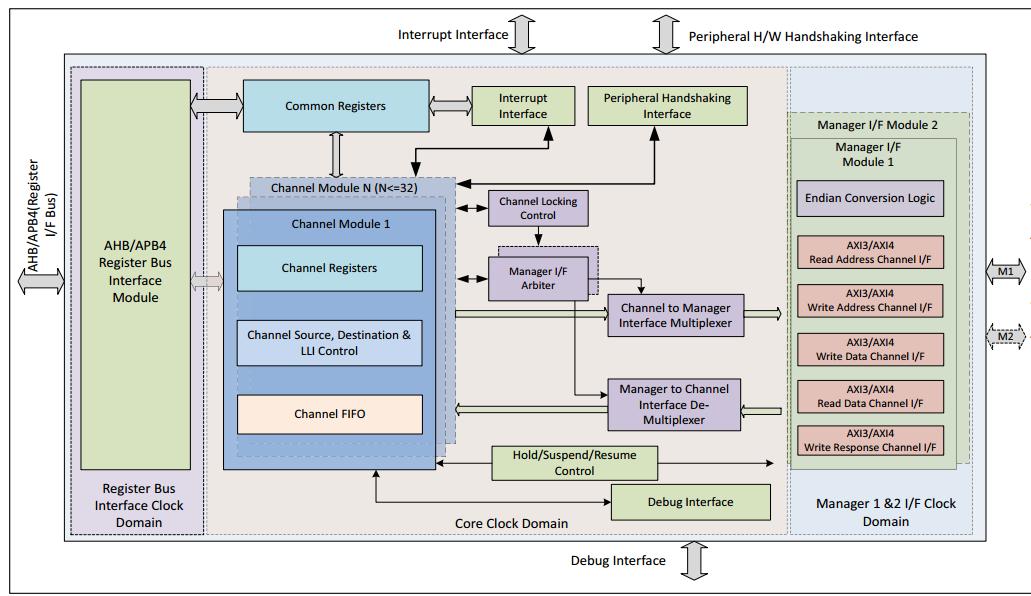

synopsys dw_axi_dmac 使用集成经验

#总体简介  AHB/APB用于寄存器配置和访问,2个AXI Master port用于实现数据src和ds ......

AMD Xilinx AXI Interrupt Controller 中断优先级

中断优先级 AXI Interrupt Controller支持中断优先级。 在Vivado Block Design中, bit-0连接的中断优先级最高, 越靠近bit-0的中断优先级最高。 AXI Interrupt Controller的手册pg099中的描述如下: Priority betw ......

第11讲 AXI_FULL自定义总线详解

DDR3 IP基础知识 (1条消息) 快速上手Xilinx DDR3 IP核 汇总篇(MIG)_ddr3 xilinx_孤独的单刀的博客-CSDN博客 DDR3_MIG_TB module top( output [31:0] c);localparam [15:0] a = 65535;local ......

AXI_LITE仿真调试

在SDK中使用xil_DCacheDisable(); 导出内存中的数据 所得的BIN文件可以用WINHEX打开 matlab代码 bin2bmp clear; clc; close; p_fid = fopen('../data/out.bin','r'); a = fread(p_fid); c ......

第2讲 AXI总线初识

axi stream 数据显示 tuser是代表本帧的第一个像素 tlast在每一行的最后一个像素拉高 AXI LITE总线写数据 AXI LITE总线读数据 AXI FULL总线写数据,64位 burst_length为16 AXI FULL总线读数据 技巧:导出ILA数据 ......

AXI DMA 设计分析

AXI DMA 架构 SBIU SBIU:Slave Bus Interface Unit。从机总线接口模块:通过外部 AHB/APB4 主机访问 DW_axi_dmac 的内部寄存器的读写控制逻辑。从机总线接口可以通过 DMAX_SLVIF_MODE 参数进行配置。 DMAX_SLVIF_MODE ......

Axis2生成wsdl客户端代码并实现webservice调用

Axis2生成wsdl客户端代码并实现webservice调用 本文地址:https://www.cnblogs.com/muphy/p/17328158.html 生成客户端代码 使用idea插件 下载axis2-idea-plugin-1.8.2.zip,官网:https://axis.apac ......

AXI4协议理解

AXI4 AXI总线是计算机内部的一种高速总线,主要用于主机(master)和从机(slave)低延迟、高速的数据传输,是由RAM公司设计的为了代替AHB、APB总线而存在的总线标准。AXI可以细分为AXI4、AXI_lite、AXI_stream。 三种总线标准的特点应用为: AXI4(AXI_f ......

ddr控制-axi4映射到altera-uniPHY

原始资料参考《emi_ddr_ug》,暂未下载到,故未粘贴datasheet原图。 **local_size:**burst 读写的最大数据数量。通常 IP 核内部有 FIFO 用于支持这样的连续数据读写,在Megafunction中设定好的最大数据数量是 Avl_size 的上限值。 **loca ......