时序 信号 行为verilog

chatGPT的js信号量实现

### 信号量类 在 JavaScript 中,可以使用 Promise 和 async/await 来模拟信号量,下面是一个简单的信号量实现: ```js class Semaphore { constructor(maxConcurrency) { this.maxConcurrency = m ......

Django信号、自定制命令、开启事务、执行原生SQL

[toc] # Django信号 ```python django自带一套信号机制来帮助我们在框架的不同位置之间传递信息。 简单的说,当某一事件发生时,信号系统可以允许一个或多个发送者(senders)将通知或信号(siganls)发送给一组接收者(receivers)。有内置信号(执行构造方法前, ......

m基于UWB信号的Rake接收性能matlab仿真,对比最大比合并,等增益合并,选择合并

1.算法仿真效果 matlab2022a仿真结果如下: 2.算法涉及理论知识概要 基于UWB信号的Rake接收性能仿真涉及了多个步骤,包括信号生成、传输、接收以及多径信道中的信号合并等。超宽带(UWB)通信技术以其大带宽、高容量和抗多径传播等优势而受到关注。Rake接收器是UWB通信系统中用于抑制多 ......

2nginx平滑升级及信号使用

nginx平滑升级及信号使用 1信号 nginx 命令支持向其发送信号,实现不同功能 nginx 当做单独命令使用有以下选项 [root@localhost ~]# nginx -h 显示帮助信息 nginx version: nginx/1.18.0 Usage: nginx [-?hvVtTq] ......

【补充】Django中的信号

# 【一】Django中的信号 - Django中的信号是一种机制,用于在特定事件发生时自动触发相关的操作或函数。 - 通过使用信号,可以实现模块间的解耦和事件驱动的编程。 - 在Django中,有两种类型的信号:内置信号和自定义信号。 # 【二】内置信号 - Django提供了许多内置信号,以便我 ......

【11.0】Flask框架之信号

# 【一】引入 - Flask框架中的信号基于blinker,其主要就是让开发者可是在flask请求过程中定制一些用户行为 # 【二】安装 ## 【1】安装 ```python pip3 install blinker ``` ## 【2】内置信号 ```python request_started ......

握手信号

verilog企业真题 VL60 使用握手信号实现跨时钟域数据传输 描述: 1)分别编写一个数据发送模块和一个数据接收模块,模块的时钟信号分别为clk_a,clk_b。 2)两个时钟的频率不相同。数据发送模块循环发送0-7,在每个数据传输完成之后,间隔5个时钟,发送下一个数据。 3)请在两个模块之间 ......

C#中扩展方法无法获得多态性的行为

在C#中,扩展方法(Extension Methods)是一种用于给现有类型添加新方法的技术。但是,扩展方法无法实现多态性的行为,因为它们是静态方法,它们的行为是在编译时确定的,而不是在运行时。 多态性是面向对象编程的一个重要概念,它允许不同的对象以不同的方式响应相同的方法调用。多态性的实现依赖于继 ......

基于Alexnet深度学习网络的ECG信号是否异常识别算法matlab仿真

1.算法理论概述 ECG信号异常识别是医学领域中的重要研究方向之一。本文将从专业角度详细介绍基于Alexnet深度学习网络的ECG信号是否异常识别算法,包括实现步骤和数学公式的详细介绍。 一、算法概述 基于Alexnet深度学习网络的ECG信号是否异常识别算法包括以下步骤: 数据预处理:对原始ECG ......

m基于FPGA的多径信道模拟verilog实现,包含testbench,可配置SNR,频偏,多径增益和多径延迟

1.算法仿真效果 其中Vivado2019.2仿真结果如下: 2.算法涉及理论知识概要 瑞利分布是一个均值为0,方差为σ²的平稳窄带高斯过程,其包络的一维分布是瑞利分布。其表达式及概率密度如图所示。瑞利分布是最常见的用于描述平坦衰落信号接收包络或独立多径分量接受包络统计时变特性的一种分布类型。两个正 ......

时序数据库 TDengine 与创意信息兼容性互认,让你的数据共享方案更丰富

涛思数据旗下时序数据库 TDengine 与创意信息旗下创意物联感知平台顺利完成兼容性互认,经过双方共同严格测试,该平台与 TDengine V3.X 版本完全兼容,为企业进一步实现高效便捷的数据共享提供了更丰富的方案。 ......

完成对工地或是工厂车间等现场作业场景中人员打电话、玩手机违规抽烟等行为实现自动检测识别,提高对生产作业地区安全风险管控。

完成对工地或是工厂车间等现场作业场景中人员打电话、玩手机违规抽烟等行为实现自动检测识别,提高对生产作业地区安全风险管控。 ......

测试DE10-Standard开发板VGA接口(基于ADV7123)输出RGB彩条时显示器显示“无信号”Signal Tap来帮忙!

Signal Tap 工具真的是一款非常非常实用的调试工具。 最近想显示VGA 三色彩条 (源码:基于友晶科技 FPGA开发板 DE2-115 和 DE10-STANDARD 的VGA彩条显示设计(ADV7123)),引 脚分配和控制信号的设计 都检查了 没有错误。也排除了VGA显示器故障(测试DE ......

常见DDos攻击行为的数据集

# 不常见的DDoS攻击数据集 ## SYN泛洪攻击 https://www.impactcybertrust.org/dataset_view?idDataset=742 University of Southern California-Information Sciences Institut ......

高速测速王牌--计讯物联4G全网通路由器,对交通违法行为零容忍

根据我国《道路安全交通法》规定,机动车在高速公路行驶,最高不得超过120km/h的时速!然而,一些司机无视高速公路的限速规则发生重大交通事故,进而导致人员伤亡和财产损失。由此可见,高速公路测速方案的应用势在必行,利用技术强制驾驶员遵守交通规则,从而将事故发生率降到最低。 行业需求 01 感知基础能力 ......

锁、递归锁、条件变量、信号量代码解析(Lock, RLock, Condition, Semaphore)

# 锁 ## Lock ```python >>> help(type(threading.Lock())) Help on class lock in module _thread: class lock(builtins.object) 锁对象是一个同步原语。 A lock object is ......

三河凡科科技飞讯教学篇:压力传感器模拟信号(频率)转数字信号的问题

压力传感器模拟信号(频率)转数字信号的问题 三河凡科科技飞讯教学篇:压力传感器模拟信号(频率)转数字信号是现代控制系统中十分重要的一个问题。在许多工业应用中,压力传感器模拟信号需要被准确地转换成数字信号,以便进行精确的控制和监测。在本文中,我们将探讨压力传感器模拟信号转数字信号的原理、方法和应用。 ......

Qt 信号槽连接源码解读

在声明信号的时候,Qt 会将信号于 QMetaThod 进行绑定,当emit 一个信号的时候, 会调用一个 QMetaMethod::invoke 函数。 查看源码, 在qmetaobject.h 中看到一个函数: bool QMetaMethod::invoke(QObject *object, ......

m基于FPGA的高斯白噪声信道模拟系统verilog实现,包含testbench,可以配置不同的SNR和频偏

1.算法仿真效果 vivado2019.2仿真结果如下: SNR=0db,无频偏 SNR=5db,无频偏 SNR=25db,无频偏 SNR=45db,带频偏 2.算法涉及理论知识概要 高斯白噪声信道在通信系统中具有重要意义,模拟此类信道有助于评估系统性能。本文提出的FPGA实现系统可以灵活地模拟不同 ......

4G模块信号强弱测试总结

wcdma_rssi(接受信号强度指示)资料依据:在CDMA网络中,RSSI的范围在-110dbm —-20dbm之间。一般来说,如果RSSI<-95dbm,说明当前网络信号覆盖很差,几乎没什么信号;-95dmb<RSSI<-90dbm,说明当前网络信号覆盖很弱;RSSI〉-90dbm,说明当前网络 ......

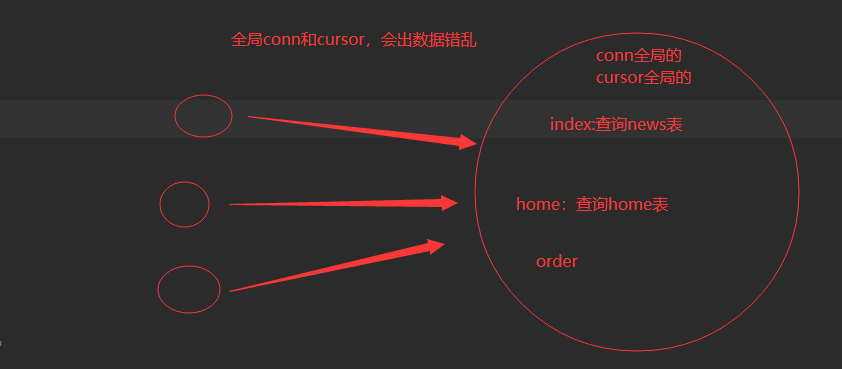

连接池、信号、flask-script

[toc] # 一 数据库连接池 ```python # flask >数据库 >原生操作 >pymsql ```  ......

lora芯片PCB电路板影响接受信号的原因汇总

Lora芯片的PCB板受力接收信号有问题可能有电路板设计问题、电路板受潮或受损、外部干扰、设备兼容性问题等原因及其解决办法... ......

Qt 信号槽管理方式

#### 连接信号槽 connect 函数的第五个参数 ConnectionType 是一个定义在 Qt namespace 中的一个枚举,具体内容如下: ```cpp enum ConnectionType { AutoConnection, DirectConnection, QueuedCon ......

Qt经典面试题:Qt信号槽机制与优势与不足

概念信号槽是 Qt 框架引以为豪的机制之一。所谓信号槽,实际就是观察者模式。当某个事件发生之后,比如,按钮检测到自己被点击了一下,它就会发出一个信号(signal)。 这种发出是没有目的的,类似广播。如果有对象对这个信号感兴趣,它就会使用连接(connect)函数,意思是,将想要处理的信号和自己的一 ......

t113-c-线程、锁、信号

线程: 这个之前的文章已经记录过了 线程之间的通信(同步) https://blog.csdn.net/weixin_56187542/article/details/126251049 锁: c的锁同样是pthread头文件里面的 https://blog.csdn.net/shaosunrise ......

高速信号处理处理卡设计原理图:501-基于TMS320C6670的软件无线电核心板

北京太速科技自主研发的TMS320C6670核心板,采用TI KeyStone系列的四核定点/浮点DSP TMS320C6670作主处理器。板卡引出处理器的全部信号引脚,便于客户二次开发,降低了硬件的开发难度和时间成本。板卡满足工业级环境应用。 ......

写Verilog通用模块的技巧----持续更新

在编写代码为了能够方便移植或者说为了一劳永逸,往往会考虑把模块代码写得更加的通用。比如可以进行传参配置,这里主要是通过位宽传参。笔者写过不少的代码,觉得写通用模块代码需要思考挺长的时间去处理数据赋值之类的,需要总结出公式才能使代码通用,为了方便查找,这里就总结下笔者常用到的一些写法,大部分的通用代码 ......

【Verilog】一文带你了解verilog基础语法

Verilog很简单,always..if..else走天下。 ——鲁迅 前言 虽说verilog很简单,简单到always..if..else走天下。 但是也会有不知道怎么写代码的尴尬场景。代码也写了不少了,回过头来,再来继续学习Verilog,整理再出发! 大概思路:基础语法——高级语法——Ve ......

行为模式 -- 观察者模式(Observer)

Observer(观察者模式) -- 对象行为型模式 ### 别名 依赖,发布-订阅(publish - subscribe) ### 意图 定义对象间的一种**一对多**的依赖关系,当一个对象的状态发生改变时,所有依赖于它的对象都得到通知并被自动更新。 ### 主要解决的问题 一个对象状态改变给其 ......