电路设计

模拟集成电路设计系列博客——2.1.5 两级放大器的系统失调电压

2.1.5 两级放大器的系统失调电压 在设计两级放大器时,如果设计者不加以注意,有可能会导致系统输入失调电压。实际上,这是许多应用在集成电路产品中的原型设计碰到的问题。为了搞清楚为什么有必要要保证没有系统输入失调电压,考虑如下图中的两级放大器,当输入差分电压为0时(即\(V_{in}^+=V_{in ......

模拟集成电路设计系列博客——2.1.4 两级放大器的摆幅

2.1.4 两级放大器的摆幅 放大器输出变化的最大速率受到其内部有限的偏置电流的限制,当放大器的输入变化过快时,放大器无法再在输入保持虚地,因此放大器会看到一个巨大的差分输入。放大器的输出随之以最大速率进行变化,称之为摆幅。在摆幅的限制下,放大器的响应是非线性的,其影响如下图所示: 中,有一个n沟道共源极管子$Q_1$和一个n沟道共栅极管子$Q_2$,这种结构也被称作 ......

模拟集成电路设计系列博客——1.2.3 共栅放大器

### 1.2.3 共栅放大器 带有有源负载的共栅级放大器如下图所示,一般这种结构用于当输入阻抗需要是一个小阻值时。例如,如果需要一个$50\Omega$的输入阻抗来匹配一个$50\Omega$的传输线。另一种共栅放大器的常见用于是用在输入信号为电流的放大器的第一阶,在这种情况下为了确保所有的电流信 ......

模拟集成电路设计系列博客——1.2.2 共漏放大器(源极跟随器)

### 1.2.2 共漏放大器(源极跟随器) 另一个电流镜的常见应用时为源极跟随器提供偏置电流,在下图的例子中,$Q_1$为源极跟随器,$Q_2$为给$Q_1$提供偏置电流的有源负载,这个结构一般用于电压缓冲器,因此也被称作源极跟随器。因为输入和输出节点分别在栅极和源极,漏极作为小信号地,这个结构同 ......

模拟集成电路设计系列博客——1.2.1 共源极放大器

### 1.2.1 共源极放大器 基本电流镜的一个常见用途时用于单管放大器的有源负载,如下图所示,共源级放大器是当需要高输入阻抗时最常见的增益级。 此处一个n沟道的共源级放大器以一个p沟道的电流镜作为有源负载提供驱动晶体管的偏置电流。通过使用有源负载来为驱动管子所需要的偏置电流。通过使用有源负载,一 ......

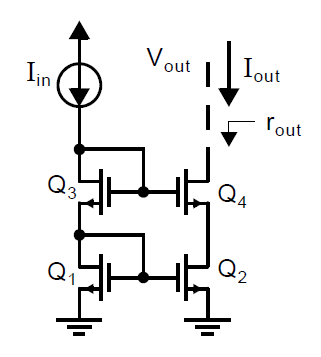

模拟集成电路设计系列博客——1.1.7 带有输出阻抗增强的宽摆幅电流镜

### 1.1.7 带有输出阻抗增强的宽摆幅电流镜 下图的结构在[Gatti, 1990],[Coban, 1994; Martin, 1994]中被提出和使用,与[Säckinger, 1990]的输出阻抗电流镜结构很像,除了一个二极管接法的晶体管被加在共源级增强放大器前作为电压转换器。  这是一个使用 ......

模拟集成电路设计系列博客——1.1.3 Cascode电流镜

### 1.1.3 Cascode电流镜 Cascode电流镜是一种高输出阻抗电流镜,其基本结构如下图所示:  首 ......

模拟集成电路设计系列博客——1.1.2 源极退化电流镜

### 1.1.2 源极退化电流镜 简单电流镜可以仅通过两根晶体管实现,其作为电流源的输出阻抗为$r_{ds2}$,为了进一步增加输出阻抗,可以使用一种源极退化电流镜,下图暂时了源极退化电流镜的结构。 、物理介质接入层(PMA)、双绞线物理介质相关子层(TP-PMD)、10BASE-TX编码器/解码器、双绞线介质连接单元(TPMAU)、MII和RMII接口等以太网 Transce ......

工业级以太网控制器CH390介绍以及应用电路参考设计

1、概述 CH390是一款自带10/100M以太网介质传输层(MAC)和物理层收发器(PHY)的工业级以太网控制器芯片,支持10BASE-T的CAT3、4、5和100BASE-TX的CAT5、6连接,支持HP Auto-MDIX,低功耗设计,符合IEEE 802.3u规范。 CH390内置16K字节 ......

设计一个1-8分频电路?要求占空比50%

请设计一个1-8分频电路,占空比50%。 这样的分频电路其中有奇分频和偶分频,需要在一个电路中实现。其中奇分频和偶分频是在输入确定的分频值下,对其进行相应的奇偶分频。 给出设计的代码&激励&仿真波形 module fenpin_8 ( input sys_clk , input sys_rst_n ......

设计一个单比特跨时钟域传输电路?从慢到快&从快到慢

Clock Domain Crossing (CDC) : 跨时钟域设计中,信号adat从aclk domain传播到bclk domain;aclk与bclk之间的频率,相位没有固定关系,为asynchronous异步关系的时钟。 分为单比特跨时钟域和多比特跨时钟域。 多比特跨时钟域:采用异步FI ......

PCB layout,或称为PCB设计,是将电子元件和连接线路等布局到电路板上的过程。

1. 设计思路 在进行PCB layout前,需要明确电路板的设计目标、功能、性能指标等,按照最终需求来设计电路板的参数、尺寸和针脚安排等。 2. 元器件部署 按照较理想的排列方式,分配和放置电子元件的位置和布局,也就是确定元器件的摆放位置、取向和连线顺序,配合特定的机械框架基本符合的要求。还要考虑 ......

设计一个小数(分数)分频电路?

请设计一个小数(分数)分频电路? 例:设计一个3.6的分频电路。 计算原理: N=M.D>1 分频 M整数部分 D小数部分 使用M分频和M+1分频 来构成 M.D分频 设M分频 A次 M+1分频 B次 可得 M*A+(M+1)*B 周期内可看作 [M*A+(M+1)*B] / (A+B)=N 分频 ......

设计一个复位电路?同步复位&异步复位

请设计一个复位电路? 复位的目的:使芯片电路处于一个已知的、确定的状态。 复位的分类:同步复位和异步复位。 同步复位:指的是当时钟上升沿检测到复位信号,执行复位操作,有效的时钟沿是前提。 同步复位的优点如下: a、有利于仿真器的仿真; b、可以使所设计的系统成为 100%的同步时序电路,有利于时序分 ......