时序 信号 行为verilog

关于Qt **QNetworkAccessManager**、**QNetworkReply**、**QNetworkRequest**实现ftp下载时,**QNetworkReply**::**downloadProgress**信号的**bytesTotal**一直为-1的原因分析

实现的ftp下载需要反馈下载进度,但是代码得到的**bytesTotal**始终为-1,直到下载完成那一刻,才变成文件大小。于是分析qt5base的network部分代码: network/access/qnetworkaccessftpbackend.cpp文件中,有如下片段: ```c++ vo ......

m基于FPGA的CRC循环冗余校验系统verilog实现,包含testbench

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: Quartusii18.0+ModelSim-Altera 6.6d S ......

m基于FPGA的AGC自适应增益控制系统verilog实现,包含testbench

1.算法仿真效果 Vivado2019.2仿真结果如下: 放大后可以看到: 2.算法涉及理论知识概要 数字AGC(Automatic Gain Control)是一种广泛应用于通信系统中的自动增益控制技术。它可以自动调节接收信号的增益,以使信号的强度保持在适当的范围内,从而保证接收到的信号质量。 数 ......

可穿戴脑电信号采集设备研发阶段总结

一 阶段梳理 脑电信号采集到现在为止,算是告一段落了。主流的研发已经结束了。大厦已经建成,后面就剩下装修了。在这里,把最近遇到的一些问题梳理一下。 二 问题梳理 关于格式转换: 该数据是24bit的,还涉及到里面的帧头转换,这里非常容易出问题。笔者在这里栽了不少跟头,这块真是考验人的基本功的。 关于 ......

buaa os lab4-challenge 信号系统的实现

# buaa os lab4-challenge 信号系统的实现 ## 信号是什么 - 生活中我们会收到各种各样的信号,比如老师在群里布置了一个新的ddl,或者肚子发出咕咕的叫声提醒我们该吃饭了,接收到信号之后我们并不是马上处理,需要等到一些合适的时机并前横利弊,比如对于人来说肯定是吃饭重要,所以我 ......

DVE 调试手段强制修改信号的值

1、修改的是DUT输入的值即只能修改激励,DUT的输出是无法修改的 2、设置Force value Freeze 代表将pready一直冻结在1‘b0的值 deposit 代表 pready 可以被subsequent驱动覆盖 3、查看设置的force值 ......

m基于FPGA的基础OFDM调制解调verilog实现,包括IFFT和FFT,包含testbench

1.算法仿真效果 其中Vivado2019.2仿真结果如下 2.算法涉及理论知识概要 正交频分复用(Orthogonal Frequency Division Multiplexing, OFDM)是一种多载波调制技术,其基本原理是将高速数据信号分成多个低速子载波,在每个子载波上调制数据,将所有子载 ......

m基于FPGA的16QAM调制解调通信系统verilog实现,包含testbench,不包含载波同步

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: Quartusii18.0+ModelSim-Altera 6.6d S ......

m基于FPGA的通信数据帧加扰解扰verilog实现,包含testbench

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: Quartusii18.0+ModelSim-Altera 6.6d S ......

m基于FPGA的QPSK调制解调通信系统verilog实现,包含testbench,不包含载波同步

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: Quartusii18.0+ModelSim-Altera 6.6d S ......

信号与系统常用的傅里叶变换和三角函数公式

傅里叶变换 $$e^{-at}u(t) \leftrightarrow \frac{1}{a+jw}$$ $$te^{-at}u(t) \leftrightarrow \frac{1}{(a+jw)^2}$$ $$|t| \leftrightarrow -\frac{2}{w^2}$$ $$\del ......

pullup和pulldown在verilog中的使用方法

### 0 前言 这段时间涉及到了IO-PAD,在IO-PAD的RTL的时候注意到了pullup和pulldown,对这个知识比较好奇,就研究了一下,顺便记录下来,IO-PAD的内容等我再研究研究再考虑记录吧 >_ NMOS`,这个过程叫`挽` 当`IN = 0`时,NMOS截止,PMOS导通,最终 ......

Qt 信号和槽出现重载的处理方法

QtCreator + Qt5.12.2 1 /* 重载信号需要注明 */ 2 connect(ui->comboBox_Mode, QOverload<int>::of(&QComboBox::currentIndexChanged), 3 this, [this](int index) 4 { ......

m基于FPGA的BPSK调制解调通信系统verilog实现,包含testbench,包含载波同步

1.算法仿真效果 vivado2019.2仿真结果如下: 对比没载波同步和有载波同步的仿真效果,我们可以看到,当不存在载波同步时,数据的包络会有一个缓慢的类正弦变换,这是由于存在频偏导致的。而当加入载波同步之后,数据的包络会存在少量起伏,但数据反转的情况已经没有了, 说明频偏得到了补偿。 2.算法涉 ......

m基于FPGA的8点DCT变换verilog实现,包含testbench,并对比matlab的计算结果

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: Quartusii18.0+ModelSim-Altera 6.6d S ......

江湖再见:毫米波雷达开发手册之行为识别应用

本文为笔者的毫米波雷达开发手册之应用DEMO开发,主要讨论笔者在研究生阶段的毫米波雷达水上行为识别工作(以及提供国内目前首个毫米波雷达水上行为识别数据集),包括本领域的研究进展剖析概述、工作成果展示等。江湖再见!Let us make millimeter-wave radar serve ever... ......

golang实现设计模式汇总-创建型 | 结构型 | 行为型

历时一个多星期的常用设计模式暂告一段落,今天汇总下使用频率较高的几种常见设计模式。 以下个人根据类型分为3种,不喜勿喷: * 创建型 * 结构型 * 行为型 ### 1.创建型 常用如下: * [单例模式](https://juejin.cn/post/7238604003599974456) * ......

m基于FPGA的FOC控制器verilog实现,包括CLARK,PARK,PID及SVPWM,含testbench

1.算法仿真效果 Quartus II 12.1(64-Bit) ModelSim-Altera 6.6d Starter Edition 仿真结果如下: 2.算法涉及理论知识概要 整个系统的结构如下所示: 1、采集到两相电流 2、经过clarke变换后得到两轴正交电流量, 3、经过旋转变换后得到正 ......

m基于FPGA的BPSK调制解调通信系统verilog实现,包含testbench,不包含载波同步

1.算法仿真效果 本系统进行了两个平台的开发,分别是: Vivado2019.2 Quartusii18.0+ModelSim-Altera 6.6d Starter Edition 其中Vivado2019.2仿真结果如下: Quartusii18.0+ModelSim-Altera 6.6d S ......

从开源到云原生,时序数据库 TDengine 六年回顾精彩纷呈

回顾 TDengine 六年发展,成长和进步跃然纸上。由小到大,由弱到强,伴随着 TDengine 影响力的逐渐扩大,涛思数据也走出了一条独具特色的创业之路。 ......

Verilog中参数化信号复位置0的写法

当前面有对某信号位宽进行参数化设定: parameter ADDR_WIDTH = 3,然后后面又需要对该信号初始化时,可以这么写: always @(posedge sys_clk or negedge sys_rst_n) begin if(!sys_rst_n) wr_ptr <= {ADDR ......

CAPL 脚本对信号收发的判断

在CAPL脚本中,您可以使用条件语句和CAN消息的收发函数来进行信号的判断和处理。以下是一些常见的CAPL脚本语句用于信号收发的判断: 1.判断消息是否收到 on message can_message { if (this.DLC > 0) // 判断接收到的消息的数据长度是否大于0 { // 执 ......

2022 中国开源创新大赛,时序数据库 TDengine 榜上有名

凭借着强大的开源创新能力和产品竞争力,时序数据库(Time Series Database) TDengine 收获了“2022 年中国开源创新大赛”二等奖的好成绩。 ......

通达信----5日均线超跌信号

MA5:=MA(C,5); XX:100*(MA5-REF(MA5,1))/REF(MA5,1),NODRAW; XXB:LLV(XX,15)<-3 AND XX>-1 AND REF(XX,1)<0; 短期的暴跌往往持续不会长久,找机会买入。 ......

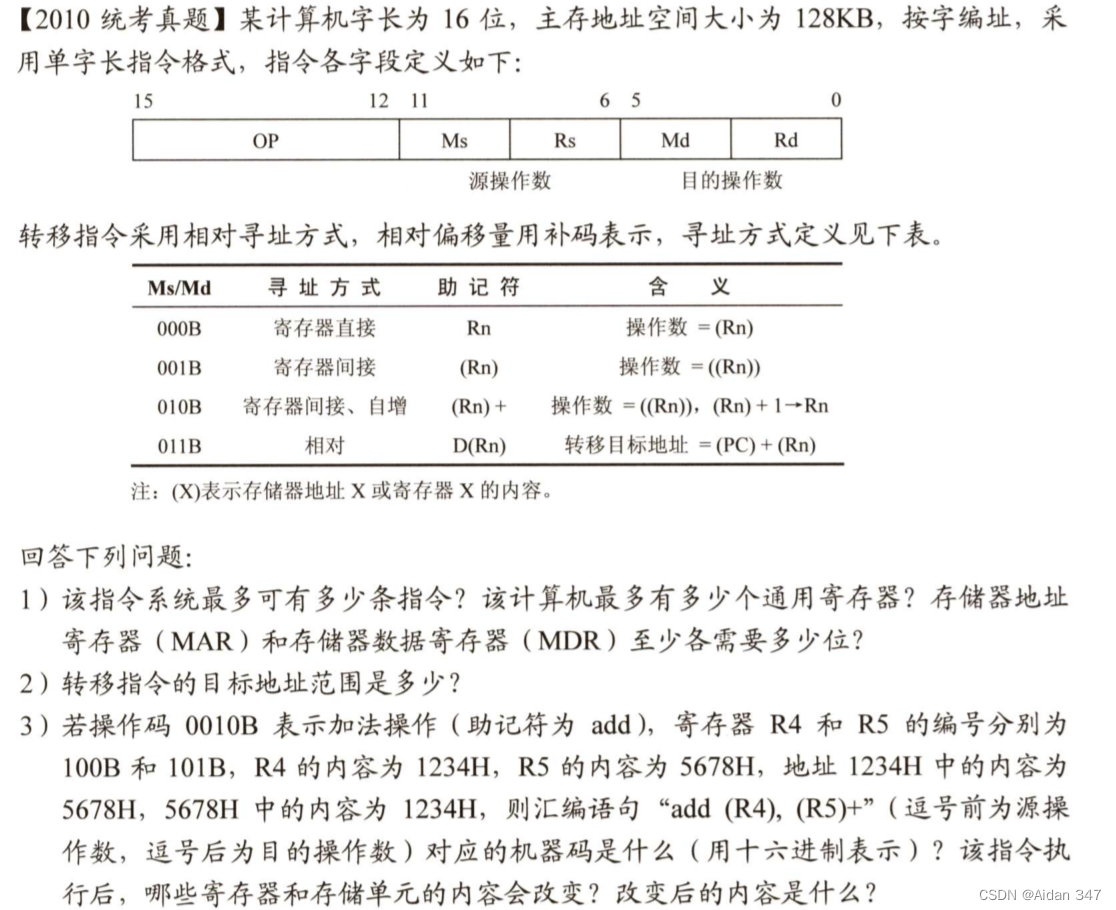

计算机组成原理:指令系统、CPU数据通路信号(例题

## ## 分析: 1. 由题目可知操作码占4位,所以支持的操作指令为$2^4$种指令 2. 操作数占6位,其中寻址3位,寄存器编号3位,所以最 ......

时序数据库 TDengine 六周年庆典活动圆满落幕,现场火爆

2023 年 6 月 6 日,在全体涛思人和一众“铁粉”的见证下,TDengine 六岁“生日趴”圆满落地啦!时光同路,信念如初。从 2017 到 2023,TDengine 已经走过六个春秋,我们的团队也从最初的 5 个人发展到了现在的 80 余人。在数字化转型的浪潮中,涛思人始终勇立潮头,以技术 ......

DIY制作隔离信号注入变压器

最近在学习模电知识,接触到了测量运放环路增益,需要使用合适的注入变压器,查找资料发现商用信号注入变压器价格昂贵,不适合个人学习使用。看到LOTO使用普通音频变压器做测试,也跟技术群友做了交流,尝试使用各种变压器、共模电感做测试,效果都不太理想。在逛某鱼时发现有位大神在出售自制的信号注入变压器,其介绍 ......

常见的进程信号

> 进程的管理主要是指进程的关闭和重启。我们一般关闭或重启软件,都是关闭或者重启它的程序,而不是直接操作进程的。比如,要重启`apache`服务,一般使用命令`service httpd restart` 重启`apache`的程序。 > > 那么,可以直接通过管理进程来关闭或重启`apache`吗 ......

记录一下这次关于死循环使用愚蠢的行为

### 在一个多线程的使用场景下,有个变量标记线程是否退出,然后我有这么一行代码 ~~~C++ while ( !stopRequest) {} ~~~ ### 这个问题是 cpu 某个核会一直占用,正确做法是在loop中 sleep 一段时间,例如 1毫秒,10毫秒,100 毫秒。 ### 让Cp ......